表2 复用模式下EHPI口读写类型指示

具体加密方式简述如下:

1)为每一块电路板指定一个128位的密钥,密钥的选择完全随机,只要不同板子不相同即可。将密钥和加密算法(DES或是其他的加密算法)烧写入MSP430的内部做为DSP boot程序的一部分。

2)使用该密钥和加密算法,将加密后的语音编解码算法的程序和数据烧写入DSP的外部存储Flash芯片之中。

3)将DSP设置成工作于HPI口boot模式,在每次重启之后,主机将一段BOOT程序装入起始位置为0x10000程序空间里(该段BOOT程序中包含了解码程序),并将128位的密钥load到DSP内部的某个特定位置。主机将DSP的RST引脚置高表示主机的load过程结束。DSP自动从0x10000的位置开始执行程序,这段程序从Flash中读入加密了的程序和数据,并使用主机写入的解密程序并结合128位的密钥进行解密,解密后的程序和数据被装载入DSP的程序和数据段内开始正常的运行。

由于每块电路板对应于一个唯一128位密钥,因此DSP的外部Flash中加密的程序和数据对于窃密者来说完全没有意义。该密钥和解密程序被保存在MSP430中,因此不可能被窃取或者复制。他们只有在主机启动的时候才被动态的load到DSP中。DSP的程序在开始执行正常的解码程序之前运行一段程序覆盖这段lood区间,于是,窃密者便无法获知启动的具体操作。

4)将比特流打包解包程序放置在MSP430中。编码时当DSP中的每一帧接收语音编成特定长度的比特流之后,就向MSP430发送一个中断请求。当收到该请求之后,MSP430通过DSP的EHPI口读入该比特流,并调整各个比特位之间的顺序。调整之后的比特流被回写入DSP的发送比特流缓冲区,并根据同步时钟传送到MODEM。同样,当DSP接收比特流缓冲区接收满一帧时,向MSP430发送中断,MSP430在接收到这个中断之后通过EHPI口读入接收比特流缓冲区内的数据,完成比特位置的重排的恢复。

这种方式可以有效的保证代码的安全性以及整个系统的保密性。对于基于开放总线的DSP系统来说,这种方式不失为一个很有效的通用的 硬件加密 方法。

www.55dianzi.com

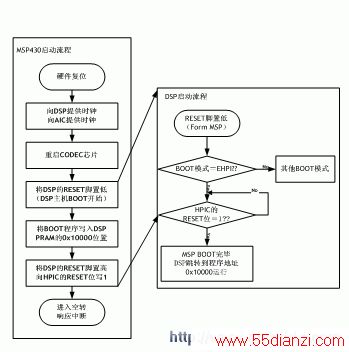

图4 MSP430和DSP启动的软件流程图

3. 低功耗 设计

本硬件平台的低功耗设计的从三方面出发,1)选择低功耗的器件。2)充分利用芯片的低功耗模式;3)动态的改变芯片的运行频率。

选用低功耗的器件:这是节省功耗的最直接的方式,现在的芯片大多通过降低内核供电电压降低功耗,现行的低功耗器件的供电电压一般都小于2V,TI的DSP大都采用两种电压驱动,内核电压1.2-1.6V,I/O电压3.3V,这既能有效的降低内核动态功耗,还能兼顾I/O的电平兼容性。TI公司的MSP430系列的MCU也是一款功耗相当低的器件,在3.3V下,其正常工作通常只需要十几个mW的供电,如果将其设置成IDLE或者睡眠模式模式,其功耗将会更低。这些都是我们选择器件重点考虑到的因素之一。

充分利用芯片的低功耗模式:[4]5510A2芯片内部划出了五个独立的IDLE域(Domain),分别负责CPU、DMA、CACHE、外设、时钟生成器、EMIF接口的配置。每个域可以独立的将该域管辖的多个部件设置成活动模式或IDLE模式以此降低DSP地功耗。针对本次设计,由于没有使用到DMA、CACHE、时钟生成器三个域中的外设,故将这三个域设置成了IDLE模式。EMIF域在DSP和MSP交换数据(为了调整发送和接收的比特流)时才被置为活动,其他时候被置为IDLE。通过这样的处理,避免了空闲的部件白白消耗能量。[5]TLV320AIC11也可以单独的将A/D和D/A部分禁用。当PTT没有按下时,表示没有话音输入,这时可以将A/D部分置为IDLE状态。同样的,当MODEM的CD信号为高的时候,表示没有有效的数字码流输入 声码器 ,故在此时可以将D/A部分设为IDLE状态。通过对着这个芯片的低功耗模式的操作,进一步降低了系统的功耗。

动态频率控制:这种方法的及根据预测的算法运算量的大小,动态的调整芯片的运行频率,从而达到节省功耗的目的。在本文设计的平台上运行的三种低速率语音编解码算法中,600bps、1200bps、2400bps的峰值运算量分别为37.4MIPS、59.2MIPS、44.8MIPS,因此将DSP的工作频率分别设置在40.096MHz、65.536MHz、49.152MHz。实验证明,这样处理能够很有效地降低DSP的内核功耗。

4. 小结

该平台具有强大的语音信号处理能力,较低的功耗以及加密等特点。实践证明,该平台在其应用场合完全达到了原先的这些设计目标,具有广阔的应用前景。

参考文献:

[1] TMS320VC5510AI DataSheet(sprs076I); TI corporation; April 2004

[2] Using the TMS320VC5510 Bootloader (spra763a); TI corporation; Mar 2002

[3] TMS320VC5510 DSP Host Port Interface (HPI) Reference Guide (spru588a); TI corporation; Feb 2004

[4] TMS320C55x DSP Peripherals Overview (spru317g); TI corporation; Feb 2004

[5] TLV320AIC11 DataSheet(slws100); TI corporation; April 2002

[6] MSP430F14x familiy Mix Signal Microcontroller DataSheet (slas272); TI corporation; Aug 2004

[7] 低功耗通用语音处理平台的设计实现; 陆希玉,詹杰,唐昆,崔慧娟;微型机与应用; 2005.7