为实现边界时钟应用,交换机设计同时实现了IEEE 1588 V1主应用和从应用。

与主机通信的端口被自动配置为从端口。嵌入式1588应用程序经从端口生成一个精确时钟,并将该时钟信息前转送到被自动配置为主端口的其它端口。与可编程定时器的紧密整合确保了该时钟与主时钟的同步精度在100ns以内。

在交换机内,每端口可最多实现两个按优先级排列的队列,以便为关键服务提供服务质量(QoS)保证。交换机还能通过编程并利用3位VLAN优先级字段、6位 DiffServ第三层代码点(IPv4)或8位服务类别(IPv6)对流量进行识别和分配优先级。

交换机设计支持IEEE 1588版本1边界和版本2透明时钟应用。可对该设计作进一步修改和强化以增加定制逻辑,例如在传统协议或PCI等不同系统接口上增加桥接应用软件,从而方便将交换机集成进现有系统。

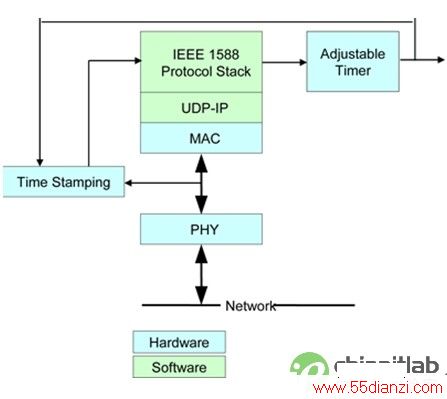

图4:包括软件和硬件在内的IEEE 1588框图

在该设计中,Nios II嵌入式处理器支持交换机的IP配置和管理,并能运行用户数据报协议(UDP)栈、IEEE 1588协议栈和精确的时序同步,并支持双路10/100 PHY收发器的PHY管理和线路诊断功能(如图4所示)。嵌入式处理器还可用于高层组网功能,如运行生成树和快速生成树算法以及终结TCP/IP链接。生成树协议 (STP)和快速生成树协议(RSTP)是链路管理协议,它们支持路径冗余,可防止网络内出现不需要的环路(要使工业以太网络正常工作,两个节点间只能有一条有效路径)。

PHY收发器

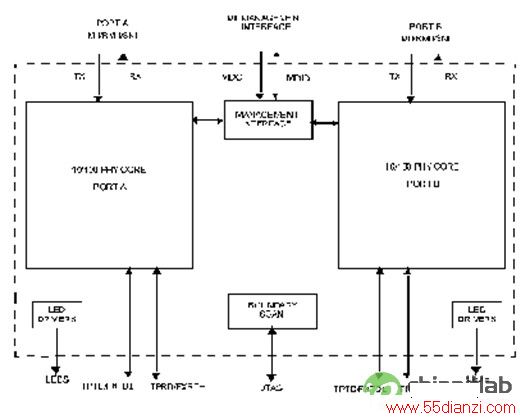

图5:美国国家半导体公司的PHY收发器框图

每个收发器都有两个完全独立的10/100Mbps端口供多端口应用使用,如图5所示。该收发器的端口切换还允许两个端口经配置提供完全集成的范围扩展、介质转换、基于硬件的快达ns级的故障切换(fail-over)以及端口监测功能。

该器件整合了用于公共工业以太网拓扑的多端口支持。特别是设计师要获得对不同应用的冗余支持,需要具备在各种条件下处理故障切换的能力。从一个网络栈切换到另一个网络栈需要不短于几百毫秒的时间,但一些应用(如 安全 应用)需要极其迅速地、最好是在PHY层实现的故障切换。该参考设计内的收发器从一个端口切换至另一个端口的时间是ns级,即使主机仍管理着控制路径。收发器信号路径中的架构改进使性能远远超过了最低PHY层规范要求,完全可以解决抖动和延时等设计问题。每个以太网PHY层由一个参考时钟驱动。为了尽量减小抖动,PHY层规范要求采用极其精确的时钟,其精度要在收发器25MHz参考时钟的50PPM以内。另外,为了满足规范要求,起始抖动必须非常小。为了解决这个问题,架构内整合了一个容忍更大抖动的机制。器件架构还针对实时以太网操作优化了延时性能,以确保把交换机延时降至最小。

在许多实时系统实现中,以太网包数据传输延时对正常的系统运作来说是个重要参数,而以太网PHY内固定或可变的发送或接收延时将成为系统延时计算中的重要组成部分。

PHY收发器的设计以限制接收数据延时的变化为出发点,这样就可提供非常确定的系统延时。

因为接收数据与接收时钟对齐,所以规避了器件接收数据时通常会遇到的非确定性因素。因此在MII和RMII模式时器件可以提供极具确定性的接收数据延时。另外,收发器能够减少发送RMII延时中常见的非确定可能性。

另一个重要的设计特性是内置的电缆诊断功能,该特性给收发器采用的传统时域反射(TDR)方法增加了前瞻性的诊断功能。新创的故障隔离功能可以借助收发器的强大信号处理能力在数据传送的同时跟踪链路质量。这种极具鲁棒性的TDR实现方法是将脉冲从接收或发送导线对送出,并观察这两个线对上的结果。通过观察每对线上的反射信号类型和强度,并通过软件计算即可确定电缆的短路和开路状况、故障点的距离,并确定哪一对有问题以及线对偏移。积极主动地监测并修正变化或恶化的链接质量可缩短系统的停歇时间,节省昂贵的维修费用。该功能还可检测安装时发生的故障,节省大量的调试工时。

本文小结

工业以太网技术一直在进步,并越来越普及,而设计师面临着对高性价比工业交换机日益强劲的需求。基于ASIC和ASSP的交换机因其架构固定,所以实际上没有余地定制出新的系统特性。为了增加特性设计一般要推倒重来,此举会导致额外的设计时间和成本支出。但如上所述的支持IEEE 1588交换机的FPGA设计可节省6到9个月的工程时间,并提供给设计师梦寐以求的灵活性,帮助他们实现精确定时协议(PTP)、 支持多个工业以太网标准、额外的标准接口或者其它可能的定制特性。