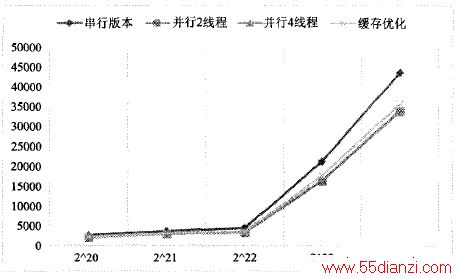

图4 算法执行时间

评价并行算法优劣还需考虑算法的负载均衡性,如表1、表2所列,缓存优化方案标准差远远小于任务并行化方案。究其原因,对于任务并行化方案而言,不同的测试数据以及划分算法(partition)对区间的划分有重要影响,从而造成任务执行时间变化范围很大;对于缓存优化方案而言,其实质是数据并行,其每一个任务都是根据缓存大小进行划分,因此每一个任务处理的数据规模基本一致,每一个任务执行的时间更确定,但由于并行任务执行完成后,需要对数据进行归并,造成一定的性能下降。

结语

本文通过对嵌入式多核处理器硬件结构的分析,从对称多处理角度对串行快速排序算法进行并行化优化,取得了很好的效果。

以ARM 双核处理器(OMAP4430)作为测试平台,从任务并行和缓存优化实现并行优化,从性能测试的结果看,任务并行具有良好的加速比,但负载均衡性差,并行线程数目不应超过物理处理器核的数目,过多的并行线程竞争处理器资源,造成性能下降。缓存优化具有良好的负载均衡性,但需要后续进行归并操作,造成性能有所下降。

总之,在嵌入式多核处理器上进行并行化优化,一方面要充分发掘嵌人式多核处理器的并行性能,提高程序的并行性;另一方面也要考虑程序算法的负载均衡性,确保在不同应用环境中程序性能一致。