2 系统软件总体设计

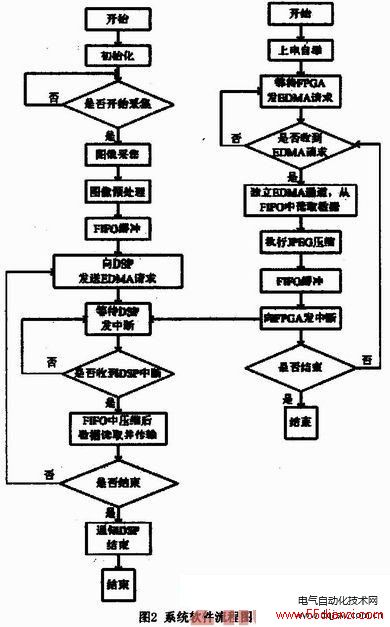

系统的软件设计根据硬件结构的总体划分,也可以分为两大部分来描述。整个系统的运行如图2所示,FPGA和DSP各自的程序独立运行,通过中断信号完成数据的实时交互。FPGA向DSP方向的指令是通过FPGA发送一个EDMA请求,DSP通过响应EDMA请求,建立EDMA通道,开始从FIFO中进行预处理后数据的读取,DSP向FPGA传输数据时,通过向FPGA发送一个中断信号,让其从FIFO中把压缩后的图像数据读出来。

如图2所示,整个系统工作流程可以简单描述如下:系统上电后,首先DSP由flash实现自举,并运行引导程序,之后转入EDMA等待状态,FPGA初始化后等待外部图像采集命令,收到图像采集命令后开始进行图像采集,并对采集到的图像进行预处理,预处理后的图像经过FIFO缓冲,在存储一定量的数据之后,FPGA通过半满信号向DSP发送EDMA请求,等待DSP响应,DSP一旦收到来自FPGA的EDMA请求,立即建立EDMA通道,从FIFO中读取数据到L2存储器,存满一帧图像后DSP开始图像压缩,等待一幅图像压缩完成之后,DSP会向FPGA发送中断信号,FPGA在收到中断信号后开始从FIFO中读取压缩后的图像数据。一帧数据读完后,判断编码信号是否有效,如果有效则按同样的规则对下一帧图像进行压缩,如果无效则通知DSP结束。

3 结论

本设计方案已经经过了硬件验证,达到了预定的设计要求,实现了大数据量的实时处理。

系统体积仅为70×70mm,功耗小于5W,中值滤波速率平均20F/S,JPEG压缩速率平均25F/s以上。不仅满足了视频处理系统的实时性要求,且体积小、功耗低,而且基于FPGA的可编程性,本系统具有良好的灵活性和扩展性。

本文关键字:暂无联系方式PLC入门,plc技术 - PLC入门

上一篇:凸轮控制器的结构与控制电路/