NS 公司的DP83640是PHYTER- IEEE 1588标准的精密时间协议收发器,为实时工业连接提供最高级的精密时钟同步,支持IEEE1588 V1和V2,支持UDP/IPv4, UDP/IPv6, 和 Layer2以太网包,以及IEEE 1588时钟同步.时间标记的分辨率为8ns,可广泛用在工厂自动化如以太网/IP与CIP同步,测试与测量,通信系统中的基站以及实时网络.本文介绍了DP83640主要特性, 功能方框图以及应用系统方框图和演示板的详细电路图.

DP83640 Precision PHYTER - IEEE 1588 Precision Time Protocol Transceiver

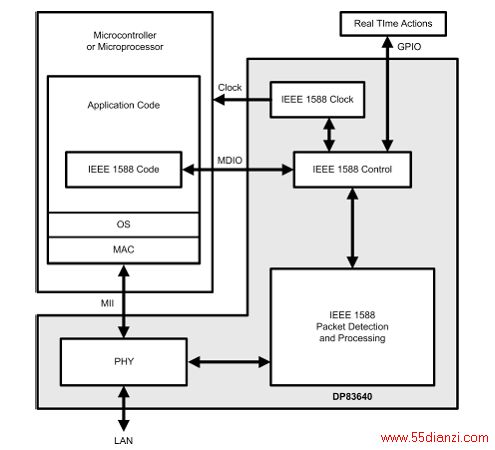

The DP83640 Precision PHYTER device delivers the highest level of precision clock synchronization for real time industrial connectivity based on the IEEE 1588 standard. The

DP83640 has deterministic, low latency and allows choice of microcontroller with no hardware customization required. The integrated 1588 functionality allows system designers the flexibility and precision of a close to the wire timestamp. The three key 1588 features supported by the device are:

―Packet time stamps for clock synchronization

―Integrated IEEE 1588 synchronized clock generation

―Synchronized event triggering and time stamping through GPIO

DP83640 offers innovative diagnostic features unique to National Semiconductor, including dynamic monitoring of link quality during standard operation for fault prediction. These advanced features allow the system designer to implement a fault prediction mechanism to detect and warn of deteriorating and changing link conditions. This single port fast Ethernet transceiver can support both copper and fiber media.

DP83640主要特性:

■IEEE 1588 V1 and V2 supported

■UDP/IPv4, UDP/IPv6, and Layer2 Ethernet packets supported

■IEEE 1588 clock synchronization

■Timestamp resolution of 8 ns

■Allows sub 100 ns synchronization to master reference

■12 IEEE 1588 GPIOs for trigger or capture

■Deterministic, low transmit and receive latency

■Selectable frequency synchronized clock output

■Dynamic Link Quality monitoring

■TDR based Cable Diagnostic and Cable Length Detection

■10/100 Mb/s packet BIST (Built in Self Test)

■Error-free Operation up to 150 meters CAT5 cable

■ESD protection - 8 kV human body model

■3.3 V I/Os and MAC interface

■Auto-MDIX for 10/100 Mbps

■RMII Rev. 1.2 and MII MAC interface

■25 MHz MDC and MDIO Serial Management Interface

■IEEE 802.3u 100BASE-FX Fiber Interface

■IEEE 1149.1 JTAG

■Programmable LED support for Link, 10 /100 Mb/s Mode,

Duplex, Activity, and Collision Detect

■Optional 100BASE-TX fast link-loss detection

■48 pin LQFP package (7mm) x (7mm)

DP83640应用:

■Factory Automation

―Ethernet/IP

―CIP Sync

■Test and Measurement

―LXI Standard

■Telecom

―Basestation

■Real Time Networking

图1.DP83640系统方框图

图2.DP83640功能方框图

图3.DP83640应用案例框图DP83640 TP&FX 演示板

The purpose of the DP83640 Demo Board is to provide National Semiconductor Corp.s customers with a vehicle to quickly design and market systems containing the DP83640. Customers are encouraged to copy EVK components to expedite their design process.

The EVK contains:

DP83640 Demo Board

Printed copy of this Users Guide

DP83640 Demo Board schematic

DP83640 Demo licensing agreement

图4. DP83640演示板外形图

图5. DP83640演示板布局图

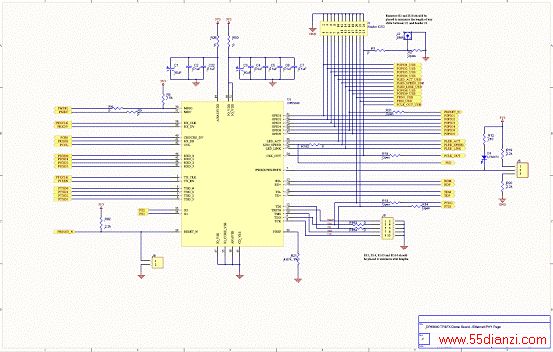

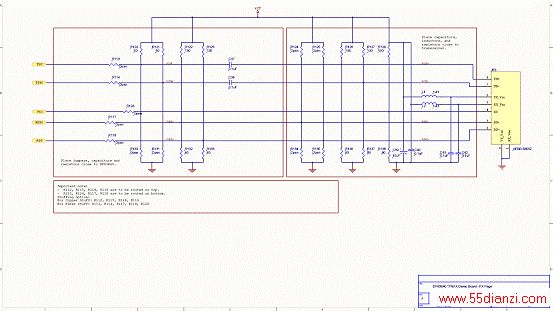

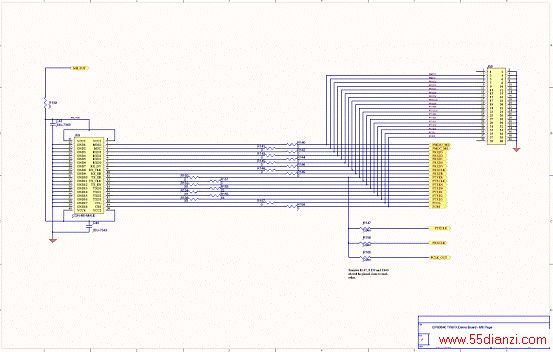

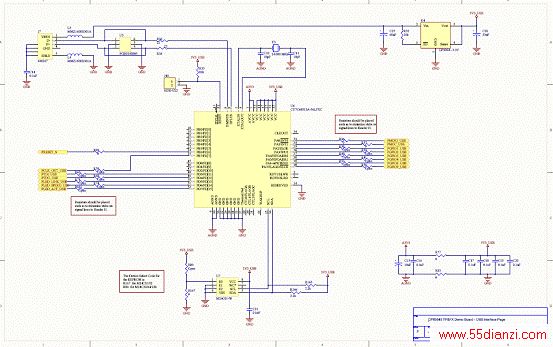

图6. DP83640演示板电路图(1)

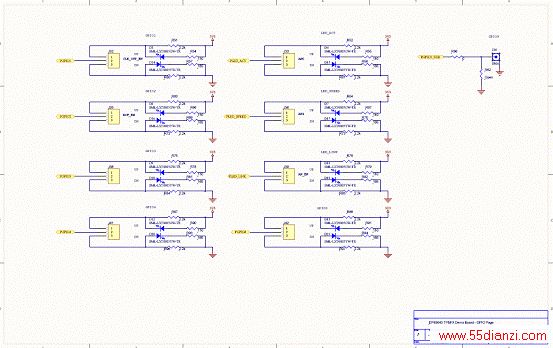

图7. DP83640演示板电路图(2)

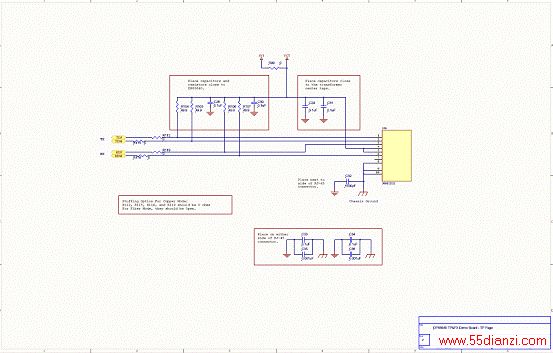

图8. DP83640演示板电路图(3)

图9. DP83640演示板电路图(4)

图10. DP83640演示板电路图(5)

图11. DP83640演示板电路图(6)

图12. DP83640演示板电路图(7)

图13. DP83640演示板电路图(8)

图14. DP83640演示板电路图(9)

本文关键字:暂无联系方式电子技术,电工技术 - 电子技术