大面积覆盖接地:在电路的工作频率较高和高速开关的数字电路中,地线不能采用条形分布,宜采用大面积覆盖的接地方式。

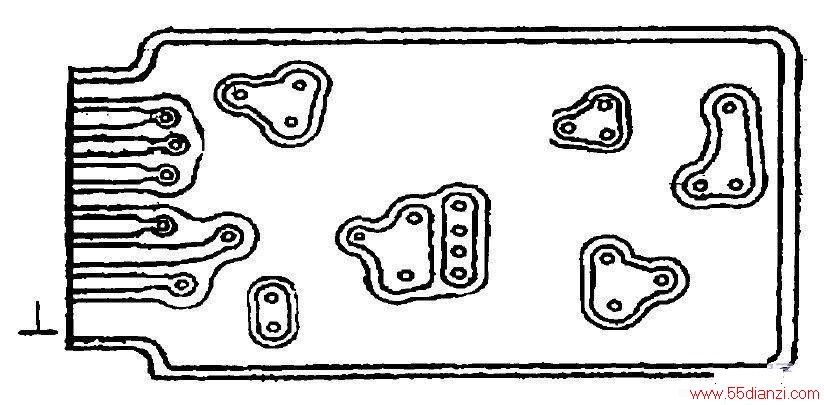

大面积覆盖地线( 如图8 所示) 是当板内导线较多时,为避免接地受导线切断而影响接地效果,而采用双面印制版,其中一面为接地用。采用大面积接地,要防止各接地元件的局部电流耦合而造成共阻抗干扰。因而对各级元件布设要尽量以本级的晶体管、集成块为中心,元件按级集中,并在本级元件的中心部位设立接地区域。

图8 大面种覆盖地线

一字形地线。当板内的级数不多时,可以采用一字形地线。各级电路可按先后顺序排列,每级电路的接地元件要相近接在地线上。板上地的引出点应放置在末级附近,如有引出至板外的输入、输出的要分开。

5 结束语

总之,在PCB 电路设计中,尤其在高频电路中必须重视共阻抗干扰的影响。只有通过良好的地线设计,合理的布局结构,才能保证电子电路工作稳定。以上对PCB 电路设计中,防止共阻抗干扰的一些方法和对策作了系统总结,供PCB 电路设计人员参考。

本文关键字:暂无联系方式布线-制版技术,电子学习 - 布线-制版技术

上一篇:电路输入阻抗、输出阻抗小结