内容摘要:多窗口显示屏控制采用μC/OS-II实时操作系统的多任务管理运行模式,各窗口视频数据由线程管理,Nios II 32位处理器作为显示屏控制器硬件系统的核心,软件系统控制多窗口任意显示。在1片FPGA上实现显示屏控制器的硬件系统,利用SOPC Builder软件定制系统所需的IP核,外扩存储设备实现视频数据的海量存储,解决了FPGA内部资源相对不足的问题。通过重构视频数据,合理组织数据的存储方式,解决视频数据的灰度控制问题,减少数据处理过程,降低了控制系统的复杂度。

关键词:μC/OS-II;Nios II;控制器;FPGA

引言

LED大屏幕显示屏是当今室外平面显示的主流,其控制系统的技术发展也日趋成熟,控制系统按数据传输方式分为两类:同步显示和异步显示。同步显示控制系统即LED显示屏和视频数据源实时保持一致,视频信号实时变化。异步显示控制系统通过USB、通用串行接口、以太网等数据通信方式,更新大屏幕控制系统的视频数据存储区。数据更新由上位机控制,LED显示屏的视频信息变化由视频数据存储区的数据决定。在异步显示系统中,可实现将显示屏分为若干区域,不同的区域对应不同的存储区,数据更新时可以只更新其中的一个或几个窗口。本设计采用嵌入式操作系统μC/OS-II的多线程控制方式,分别控制各个窗口的数据区域,实现单屏幕多窗口的任意位置显示,使得显示方式更加灵活方便。

1 系统总体设计

采用SOPC技术在FPGA上构建Nios II软核作为LED显示控制系统的处理器,实现32位的嵌入式系统操作。通过基于μC/OS-II的嵌入式操作系统的软件设计,完成对DVI视频显示数据的接收和预处理。扫描电路接收视频数据后进行存储,同时将数据进行再组织并送往扫描屏。

1.1 系统硬件结构

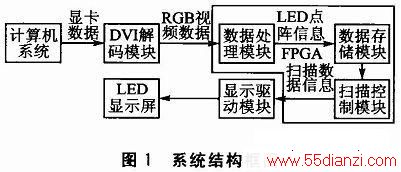

多窗口显示屏控制系统的结构框图如图1所示。

计算机显卡数据通过DVI接口将数据传送给显示屏控制系统的解码电路部分,DVI解码芯片将获得的视频数据解码,得到RGB视频数据和控制信号。控制信号中包含行扫描信号和场扫描信号,显示屏控制系统根据场扫描信号判断采集1帧视频数据是否结束,并将视频数据写入发送系统的数据存储器RAM进行缓存。FPGA从RAM存储器中读取数据,将该数据按照灰度级分为8个区域模块进行重新组织、转换,然后通过移位串行时钟送入LED显示屏进行显示。本系统的数据处理模块、数据存储模块、扫描控制模块3部分均在FPGA上实现。

1.2 软件总体设计

全彩色LED大屏幕数据量大,本设计将显示屏从逻辑上划分为多个窗口,软件部分基于μC/OS-II嵌入式操作系统编程实现。μC/OS-II操作系统的任务调度算法比较先进,在显示系统中,可以将每个窗口的显示操作都交给某个任务来执行,这样可以从很大程度上提高整个系统的运行速度和软件的可靠性。

软件基于Nios II IDE开发完成,应用程序基于μC/OS-II实时操作系统实现。软件主要由2个任务和1个定时器中断服务程序组成,任务间采用信号量的方式进行通信。计算机系统的显卡数据经DVI解码模块解码后得到RGB视频数据。任务1接收RGB视频信息,并对视频信息进行滤波、数据的位组合、数据存储区的重新组合等处理操作。任务2从内存中读取数据,并进行分析处理,把分析处理完的数据送往扫描控制模块。利用μC/OS-II的实时性和多任务的特点,采用嵌入式文件系统进行数据管理。

2 控制器的硬件部分设计方案

2.1 视频数据解码模块分析

采取从显卡的DVI接口获取数据,经过视频控制系统进行适当的数据变换,再发送到LED显示屏上显示。此模块用来获取视频源数据,完成对显卡DVI接口传输的TMDS编码数据的接收。通过TMDS解码,实现对RGB视频数据和像素时钟CLOCK、像素有效信号DE、行同步信号HSYN、场同步信号VSYN、同步检测信号SCDT等视频显示控制信号的恢复。

计算机显卡输出的DVI差分信号不能直接作为LED的扫描数据信号,需要经过解码,将该信号恢复为数字视频数据RED[7..0]、GREEN[7..0]、BLUE[7..0]等像素信息,还需要恢复控制信号,如行同步信号HSYNC、场同步信号VSYNC、数据使能信号DE和时钟CLK等控制信

息。需要一个解码电路对DVI差分信号进行解码,本设计采用TFP401A DVI解码芯片实现该功能,解码后的数据信息用于提供给LED屏控制器使用。

2.2 数据的存储组织模块分析

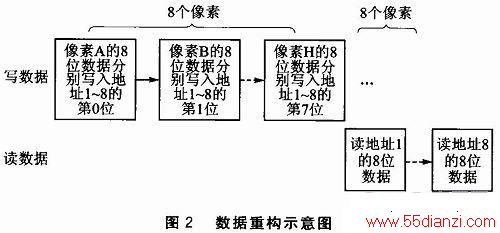

数据写入SRAM存储器中的组织方式有两种:位平面法和组合像素法。位平面法是指像素的每一位分别存放在不同的存储设备中;组合像素法是指画面上每个像素的所有位均集中存放在单个存储设备中。LED屏像素数据每一位的权值是不同的,高位的权值高,也就意味着高位为1时LED的点亮时间要长。根据两种存储结构的特点,对于LED屏,采用位平面结构有利于提高LED屏的显示效果,从而更容易实现D/T(data to time)转换。位平面法的数据需要重新组织,利用位平面结构有利于提高LED屏的显示效果。数据重构示意图如图2所示。

数据重构后,通过QUARTusⅡ软件编译,得出如图3所示仿真波形。其中,当col为1时,表示已写完上面8个地址的数据,此时读地址计数器开始计数。datain为串行输入数据,dout为串行输出数据。

2.3 扫描控制模块

将数字视频信号进行缓存处理,并将RGB信号通过脉宽调制(PWM)转换为供LED显示所需的信号送往扫描模块。扫描控制模块由用户自定义的PWM IP核和显存组成,显存采用1片SRAM实现,用来保存当前显示的1帧点阵信息数据。PWM模块通过Avalon总线和Nios IICPU连接,将从CPU接收到的数据按指定地址写入显存,然后再按一定的寻址方式从显存中读取点阵信息数据进行扫描。

2.4 其他功能模块

串口控制器、定时器、存储器控制器通过SOPC Builder软件定制集成IP核自动生成。

3 控制系统软件部分设计

该操作系统利用高效任务调度算法调度每个任务,而每个窗口的显示由单个任务完成。

3.1 数据结构

数据在存储器中的存储形式直接影响数据的存取速度和控制的复杂度,本系统对显存中的数据和缓存区的数据均重新组织,降低了数据处理和扫描控制复杂度。

3.1.1 显存数据的组织

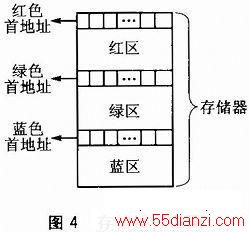

LED显示屏的每个像素点都包括红、绿、蓝3种基色,每种颜色的灰度级均为256级,即由8位数据对像素点灰度级进行编码,故每个像素点需要占用3字节的存储空间。显示时,每个像素的红管、绿管、蓝管是同时点亮的,也就是说,3种颜色的数据是并行上屏的。据此,可将红绿蓝3种颜色对应的数据分开存储,以方便操作。数据存储方式如图4所示。每种颜色的数据集中存放在某个区中,每个区域的首地址作为3种颜色的基址,在进行数据存放时,每个像素点只需给出相对变化地址(变址),然后加上不同的基址就可以在3个区域中找到对应点的视频数据。

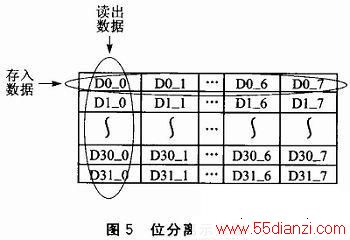

LED显示屏灰度的实现方法,是分权重扫描的。这样就需要把颜色数据位分离,然后同权重的位重新组合。为了方便操作,存储时把图4所示的分区中的每个区再分为8个权重区,所有同权重的数值集中放于对应权重区中。所谓位分离就是把数据的高低位按权重分开,然后重新组织。位分离的实现在可编程逻辑器件中也比较容易实现,可以划出一块逻辑矩阵,操作时横向存入,纵向读出即可。位分离示意图如图5所示。

3.1.2 缓存数据的组织

若要进行特技效果显示,则当前显示的数据帧和下一个数据帧存在着某种变换关系,由于CPU只能对显存进行写操作,所以需在缓存中划分出一块大小和显存相等、地址一一对应的区域screen,用于存储当前显示的数据帧信息。如果各窗口之间存在重叠现象,且特技数据处理运算直接在screen区域进行,则窗口重叠部分信息可能发生混乱。故在缓存中再为每一个窗口划分出一块存取空间(part 1,part 2,…,part n),用于存储本窗口显示的前一帧数据信息。在特技数据处理运算时,先在part区域处理各窗口的数据信息,然后将转换完的数据送往各窗口在screen区域所对应地址的存取空间,最后将screen中的数据写入地址对应的显存,从而完成显示。

3.2 软件设计