摘要:以现场可编程逻辑器件(FPGA)为设计载体,以硬件描述语言(VHDL)为主要表达方式,以QUARTusⅡ开发软件和GW48EDA开发系统为设计工具,给出了一种出租车计费器的工作原理和软硬件实现方法。同时对该出租车计费器进行时序仿真和硬件验证。

关键词:出租车计费器;FPGA;VHDL;QuartusⅡ

O 引言

随着人民生活水平的提高。以车代步已成为很多人的出行方式;而在选择交通工具时,很多人倾向于方便快捷的出租车。基于EDA技术设计的出租车计费器,以其价格便宜、安全可靠、使用方便等优点,而受到人们的普遍关注。本文以现场可编程逻辑器件(FPGA)为设计载体,以硬件描述语言(VHDE)为主要表达方式,以QuartusⅡ开发软件和GW48EDA开发系统为设计工具设计的出租车计费器,能够实现起步定价、行驶计费和等待计费等功能,完全能够满足出租车计费的要求。

l 出租车计费器的主要功能

出租车计费器能够实现的功能主要包括计费和显示两项功能。

一般费用的计算是按行驶的里程和等待时间收费。设出租车的起价为7.00元,当里程小于3km时,按起价计算费用;当里程大于等于3 km时按每公里2.5元计费。等待累计时间大于等于4min时,按每分钟1.8元计费。所以,总费用应按下式计算:

总费用=起始费用+(里程-3 km)×里程单价+(等候时间-4 min)×等候单价

显示功能的主要显示行驱里程、等候时间和总费用。其中显示汽车行驶里程用两位数字显示,显示方式为“××”,单位为km。计程范围为0~99 km,计程分辨率为1 km;而显示等候时间用两位数字显示分钟,显示方式为“XX”。计时范围为0~59 min,计时分辨率为1 mi-n;最后显示总费用用四位数字显示,显示方式为“XXX.X”,单价为元。计价范围为0~999.9元。计价分辨率为0.1元。

2 计费器结构和工作原理

2.1 出租车计费器的整体结构

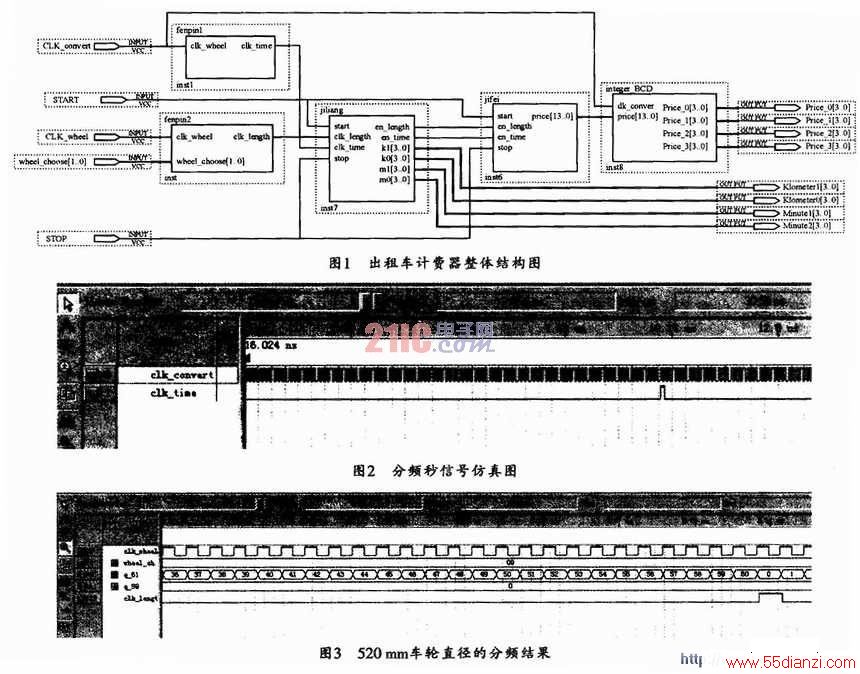

出租车计费器的整体结构如图1所示,它包括分频器模块、计量模块、计价模块和整数转换BCD模块等。

2.2 分频模块的设计

鉴于GW48EDA开发系统仅有两个时钟输入端口,而系统需要三个时钟,且各个时钟信号的频率不同,故需要对已有的时钟信号进行分频操作。

www.55dianzi.com

图2所示为分频得到的秒信号仿真图,其输入信号是整数转换为BCD码的转换信号。该转换信号频率要求非常高,这样可保证整数转换BCD

码时输出与输入不会产生太大的延时。仿真结果证明,该设计是正确的。

图3给出了分频得到的车轮走100米的输出信号,其输入信号为驱动车轮转动信号。因为对不同车轮直径,车轮走100米所需圈数不同,所以,对不同车轮进行分类讨论。图3所示的仿真波形为车轮直径是520 mm的分频结果。

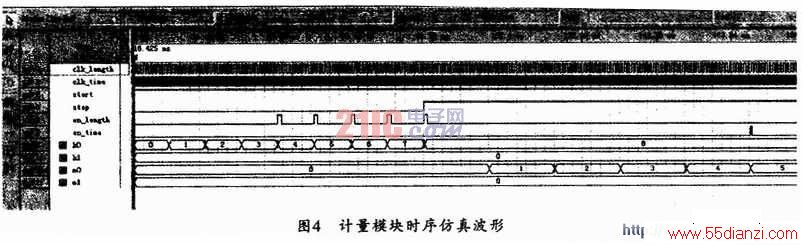

2.3 计量模块设计

根据出租车计费器的功能设计要求,费用的计算是按行驶的里程和等待时间来收费。当行驶里程小于3 km时,按起价计算费用;当里程大于等于3 km时每公里按2.5元计费。另外,等待累计时间大于等于4 min时,应按每分钟1.8元计费。因此应按要求设计行驶计费使能信号clk_length和等待计费使能信号clk_time。图4所示是这两种信号的仿真波形图。由图4可知,当出租车启动信号start为高电平有效,而等待信号stop为低电平无效时,出租车处于行驶状态,当行驶的里程数大于等于3公里时,系统将产生有效的行驶计费使能信号;而当出租车启动信号start为高电平有效,且等待信号stop也为高电平有效时,出租车处于等待状态,当等待时间大于等于4分钟时,即可产生有效的等待计费使能信号。

在此要特别说明的是,因为QUARTusⅡ综合器不支持小数,因此,在设计出租车费用的时候,应将人民币角这个单位放在个位,元放在十位。依次类推,这样便于综合器进行综合。

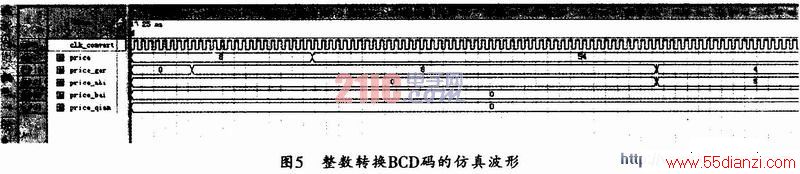

2.4 转换模块的设计

由于出租车最终的价格要由7段数码管来显示,而7段数码管的输入信号为高电平‘l’或低电平‘0’:且该设计的前面部分将价格的数据类型定义为整数,因而需要附加整数到BCD码的转换电路。图5所示为整数转换BCD码的仿真波形。由图5可以看出,当整数类型的价格(pri-ce)为8时,经过8个时钟周期,BCD码的个位就变为8;而当价格(prICe)为54时,经过54个时钟周期,BCD码的个位变为4,BCD码的十位变为5。在此需要说明的是,图5中的整数转变为BCD码需要一段时间的延时,整数数据越大,转化输出产生的延时就越大。为了实时的实现整数到BCD码的转化,需要提高转换的时钟信号频率(clk_convert)。在图2中设计的100分频的频率计,目的就是减小这一时间。在实际的应用中,还可以考虑提高clk_convert的频率,设计更高的分频倍数。

3 出租车计费器的硬件验证

本设计选用杭州康芯电子有限公司生产的GW48EDA系统作为硬件验证系统,同时选用ALTEra公司的EPlK30TCl44-3作为主控芯片。该主控芯片是一种基于查找表结构的现场可编程逻辑器件,它的基本逻辑单元是可编程的查找表。它能够实现组合逻辑的运算,而可编程寄存器则可实现时序逻辑运算。因此,只要对出租车计费器整体设计中的输入输出引脚作引脚锁定,然后重新编译和下载,就可以进行出租车计费器的硬件验证。实验表明:本设计能够实现出租车计费器的全部功能,从而证明设计是正确的。

4 结束语

本文以现场可编程逻辑器件(FPGA)为设计载体,以硬件描述语言(VHDL)为主要表达方式,以QuartusⅡ开发软件和GW48EDA开发系统为设计工具,从而设计出具有起步定价、行驶计价和等待计价功能的出租车计费器。结果表明,本设计能够实现所要求的全部功能。同时,因为

FPGA芯片体积小,功耗低,价格便宜,安全可靠,稍加修改就可以改变起步的价格、每公里行驶的价格和等待时间的价格等,而且维护和升级比较方便,也很容易做成ASIC芯片,因而具有较好的应用前景。

上一篇:基于CAN总线的电力集中抄表系统